مقدمه

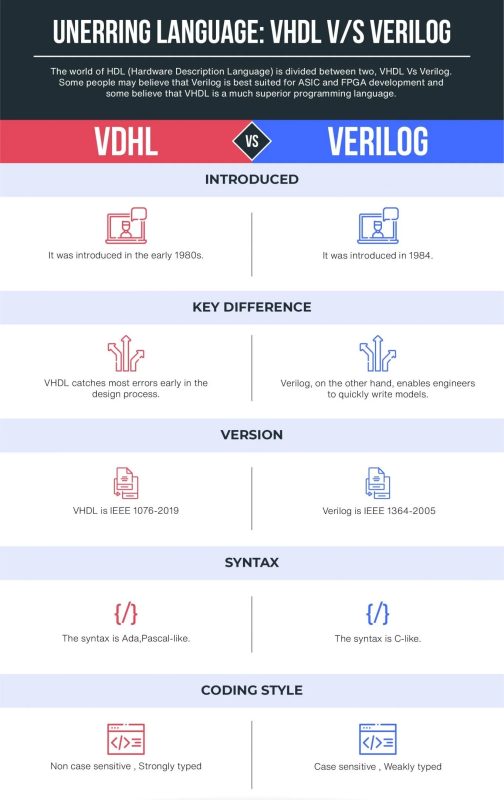

زبانهای توصیف سختافزار (HDL) مانند VHDL و Verilog، ابزارهایی هستند که برای طراحی و شبیهسازی مدارهای دیجیتال استفاده میشوند. انتخاب یکی از این زبانها برای پروژههای FPGA و ASIC یکی از تصمیمات کلیدی در دنیای طراحی سختافزار است. در این مقاله، به مقایسه این دو زبان پرداخته و ویژگیها، مزایا، معایب و موارد استفاده هرکدام را بررسی خواهیم کرد.

بخش اول: معرفی زبانهای VHDL و Verilog

VHDL چیست؟

VHDL مخفف “VHSIC Hardware Description Language” است که در ابتدا توسط وزارت دفاع ایالات متحده آمریکا برای توصیف مدارهای دیجیتال طراحی شد. VHDL زبانی ساختارمند و شبیه به زبانهای برنامهنویسی سنتی مانند Ada است. این زبان به طور گستردهای در پروژههای حساس و حیاتی مانند هوافضا و دفاع استفاده میشود.

ویژگیهای کلیدی VHDL:

- ساختار بسیار دقیق و رسمی

- بسیار مناسب برای پروژههای بزرگ و پیچیده

- قابلیت استفاده از انواع دادههای مختلف

- پشتیبانی قوی از توصیف همزمانی و ترتیبگذاری مدارها

Verilog چیست؟

Verilog یک زبان توصیف سختافزار دیگر است که به دلیل سادگی و شباهت بیشتر به زبانهای C-like بسیار محبوب شده است. این زبان در دهه 1980 توسط شرکت Gateway Design Automation توسعه داده شد و به یکی از زبانهای استاندارد طراحی دیجیتال تبدیل شد.

ویژگیهای کلیدی Verilog:

- یادگیری و استفاده سادهتر نسبت به VHDL

- مناسب برای پروژههای کوچکتر یا کمتر پیچیده

- پشتیبانی قوی از کتابخانههای استاندارد

- شباهت به زبانهای برنامهنویسی مانند C

بخش دوم: مقایسه ساختار و سینتکس

1. سینتکس (Syntax)

VHDL به دلیل ساختار دقیق و رسمی خود، نیاز به تعریف دقیقتر و صریحتر تمام اجزای مدار دارد. از طرفی، Verilog دارای سینتکس کوتاهتر و شباهت زیادی به زبان C است.

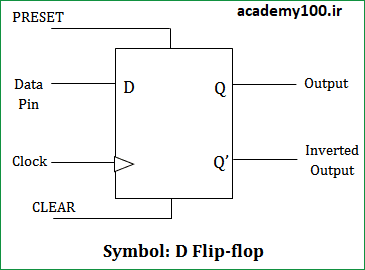

نمونه کد VHDL برای یک فلیپ فلاپ D:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity D_FlipFlop is

Port ( D : in STD_LOGIC;

Clk : in STD_LOGIC;

Q : out STD_LOGIC );

end D_FlipFlop;

architecture Behavioral of D_FlipFlop is

begin

process(Clk)

begin

if rising_edge(Clk) then

Q <= D;

end if;

end process;

end Behavioral;

نمونه کد Verilog برای یک فلیپ فلاپ D:

module D_FlipFlop (input D, input Clk, output reg Q);

always @(posedge Clk)

begin

Q <= D;

end

endmodule

همانطور که مشاهده میشود، کد Verilog به دلیل سینتکس کوتاهتر، سادهتر و خواناتر است، اما VHDL به دلیل جزئیات دقیقتر، کنترل بیشتری روی فرآیند طراحی دارد.

2. نوع دادهها

VHDL از سیستمهای نوع داده قویتری نسبت به Verilog استفاده میکند. به عنوان مثال، VHDL از انواع دادههایی مانند bit, boolean, integer و real پشتیبانی میکند، در حالی که Verilog به طور کلی از نوع دادههای بیت و بردار بیت پشتیبانی میکند.

بخش سوم: قابلیتهای همزمانی و شبیهسازی

1. قابلیتهای همزمانی (Concurrency)

یکی از ویژگیهای مهم زبانهای توصیف سختافزار مانند VHDL و Verilog، پشتیبانی از طراحی همزمان (concurrent design) است. در مدارهای دیجیتال، چندین سیگنال و فرآیند بهصورت همزمان تغییر میکنند و این زبانها باید بتوانند این تغییرات را شبیهسازی و مدیریت کنند. توانایی زبان در مدیریت همزمانی سیگنالها یکی از عوامل کلیدی برای اجرای موفق یک طراحی است.

VHDL و همزمانی:

VHDL به دلیل ماهیت ساختاریافتهاش، برای مدیریت همزمانی بسیار قدرتمند است. این زبان از بلوکهای فرآیند (Processes) برای کنترل همزمانی در سطوح مختلف استفاده میکند. بهعنوان مثال، در VHDL میتوان چندین فرآیند را تعریف کرد که بهطور همزمان در حال اجرا هستند و به تغییرات سیگنالها در زمان واقعی واکنش نشان میدهند. در طراحیهای پیچیده، این امکان به مهندسان اجازه میدهد تا همزمانی دقیقتری را در سیستم کنترل کنند.

process(clk, reset)

begin

if reset = '1' then

q <= '0';

elsif rising_edge(clk) then

q <= d;

end if;

end process;

در این مثال، فرآیند مربوط به کلاک و ریست بهطور همزمان عمل میکند. در هر تغییر لبه کلاک، بررسی و تغییر سیگنال انجام میشود، که این یک مثال از شبیهسازی همزمانی در VHDL است.

Verilog و همزمانی:

در Verilog نیز پشتیبانی از همزمانی وجود دارد اما رویکرد سادهتری در مدیریت آن ارائه میدهد. در Verilog از بلوکهای always برای مدیریت فرآیندهای همزمان استفاده میشود. این بلوکها در پاسخ به تغییرات سیگنالهای ورودی اجرا میشوند.

always @(posedge clk or posedge reset)

begin

if (reset)

q <= 0;

else

q <= d;

end

همانطور که در این کد Verilog مشاهده میکنید، همزمانی در Verilog با استفاده از حساسیت به لبه کلاک و ریست انجام میشود، که مشابه VHDL است اما سینتکس آن سادهتر است.

نتیجهگیری:

اگر به کنترل دقیقتر و پیشرفتهتر همزمانی نیاز دارید، VHDL به دلیل ساختار دقیقتر و جزئیات بیشتر در تعریف فرآیندها، گزینه بهتری است. اما اگر به دنبال سینتکس سادهتر و پیادهسازی سریعتر هستید، Verilog مناسبتر خواهد بود.

بخش چهارم: ابزارهای شبیه سازی

1. ابزارهای طراحی و شبیهسازی

ابزارهای متعددی برای هر دو زبان در دسترس هستند که برخی از محبوبترین آنها عبارتاند از:

- برای VHDL: ModelSim، Xilinx ISE، Quartus II

- برای Verilog: Synopsys, Cadence, Vivado

هر دوی این زبانها توسط ابزارهای پیشرفته FPGA و ASIC پشتیبانی میشوند، اما برخی ابزارها مانند Xilinx Vivado، پشتیبانی بهتری از Verilog ارائه میدهند.

بخش پنجم: کاربردها

1. VHDL در صنایع حساس

VHDL بیشتر در پروژههای حساس و بحرانی مانند هوافضا، مخابرات، و صنایع دفاعی استفاده میشود. دلیل این موضوع دقت بالای این زبان و قابلیت کنترل کامل بر روی جزئیات طراحی است.

2. Verilog در پروژههای صنعتی و تجاری

Verilog به دلیل یادگیری سادهتر و همچنین زمان طراحی کوتاهتر، بیشتر در پروژههای صنعتی و تجاری استفاده میشود. شرکتهای کوچکتر و تیمهای طراحی سریع معمولاً از Verilog استفاده میکنند.

بخش ششم: مزایا و معایب

1. مزایا و معایب VHDL

- مزایا:

- دقیق و رسمی

- مناسب برای پروژههای بزرگ و پیچیده

- قابلیت پشتیبانی از انواع دادههای پیچیده

- معایب:

- پیچیدگی سینتکس

- زمان بیشتر برای یادگیری

2. مزایا و معایب Verilog

- مزایا:

- ساده و قابل فهم

- سریعتر برای یادگیری و استفاده در پروژههای کوچک

- سینتکس کوتاهتر و خواناتر

- معایب:

- کنترل کمتر بر جزئیات

- مناسبتر برای پروژههای کوچکتر و سادهتر

بخش هفتم: انتخاب نهایی

انتخاب بین VHDL و Verilog به نوع پروژه و نیازهای خاص شما بستگی دارد. اگر پروژه شما پیچیده، حساس و نیازمند دقت بالا است، VHDL گزینه بهتری خواهد بود. اما اگر به دنبال زبان سادهتر با زمان توسعه کوتاهتر هستید، Verilog ممکن است برای شما مناسبتر باشد.

نتیجهگیری:

در نهایت، VHDL و Verilog هر دو ابزارهای قویای برای طراحی دیجیتال هستند و انتخاب بین آنها باید بر اساس نیاز پروژه، مهارتهای تیم و ابزارهای موجود انجام شود.