در دنیای مدارات منطقی، نیم جمع کننده و تمام جمع کننده به عنوان بلوکهای پایه در طراحی مدارات دیجیتال، اساسی هستند. در این پست، این مدارها با استفاده از verilog، که یک زبان برنامهنویسی در حوزه طراحی مدارات می باشد، پیاده سازی میشوند. وریلاگ این امکان را فراهم میکند که با انعطافپذیری و دقت بالا، نیم جمع کننده و تمام جمع کنندههای بیتی را بهسادگی توسط کد طراحی و شبیهسازی کنید. در این مقاله پیاده سازی جمع کننده با وریلاگ مورد بررسی قرار میگیرد.

کد مدار نیم جمع کننده یا halfadder

مدار نیم جمع کننده (half adder) یک مدار منطقی است که دو عدد باینری تک بیتی را با هم جمع می کند و دو خروجی دارد. یکی جمع دو ورودی یا همان Sum و دیگری رقم نقلی خروجی یا همان Carry.

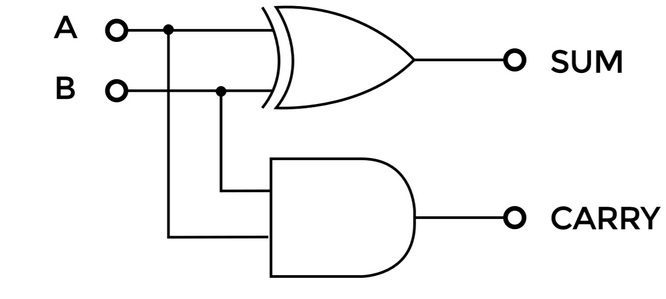

مدار نیم جمع کننده از دو گیت منطقی XOR و AND ساخته می شود. خروجی گیت XOR برابر با حاصل جمع (Sum) و خروجی گیت AND برابر با بیت نقلی خروجی (Carry) است.

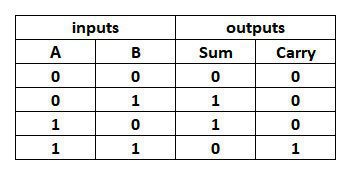

جدول درستی مدار نیم جمع کننده به صورت زیر است:

مدار نیم جمع کننده به این صورت است:

پیاده سازی ماژول نیم جمع کننده با وریلاگ verilog

در ادامه ماژول نیم جمع کننده پیاده سازی شده است. در این کد:

A و B به عنوان ورودیهای دو بیتی تعریف شدهاند.

Sum و Carry به عنوان خروجیها تعریف شدهاند.

عملگر XOR برای محاسبه حاصل جمع بیتها (Sum) استفاده شده است.

عملگر AND برای محاسبه رقم نقلی (Carry) استفاده شده است.

module HalfAdder(A, B, Sum, Carry);

input A, B;

output Sum, Carry;

xor(Sum,A,B);

and(Carry,A,B);

endmodule

پیاده سازی test bench نیم جمع کننده

تست بنچ یک بخش از محیط طراحی مدارات دیجیتال است که برای اعتبارسنجی و اجرای آزمونهای صحت مدارات ایجاد میشود. این فایل شامل تعیین ورودیها، شبیهسازی ماژولها، و نمایش نتایج است، که به مهندسان کمک میکند تا عملکرد صحیح و مطابق با نیازها را تأیید کنند.

تست بنچ ماژول نیم جمع کننده به این صورت است:

module HalfAdder_tb;

reg A, B;

wire Sum, Carry;

// فراخوانی ماژول نیم جمع کننده

HalfAdder UUT(.A(A), .B(B), .Sum(Sum), .Carry(Carry));

// تعیین ورودیها

initial begin

A = 0; B = 0; #10

$display("A=%b, B=%b, Sum=%b, Carry=%b", A, B, Sum, Carry);

A = 0; B = 1; #10

$display("A=%b, B=%b, Sum=%b, Carry=%b", A, B, Sum, Carry);

A = 1; B = 0; #10

$display("A=%b, B=%b, Sum=%b, Carry=%b", A, B, Sum, Carry);

A = 1; B = 1; #10

$display("A=%b, B=%b, Sum=%b, Carry=%b", A, B, Sum, Carry);

end

endmodule

خروجی به این صورت است:

A=0, B=0, Sum=0, Carry=0

A=0, B=1, Sum=1, Carry=0

A=1, B=0, Sum=1, Carry=0

A=1, B=1, Sum=0, Carry=1

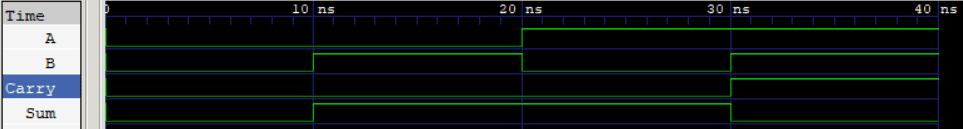

همچنین شکل موج خروجی ها به این صورت است:

کد مدار تمام جمع کننده یا fulladder

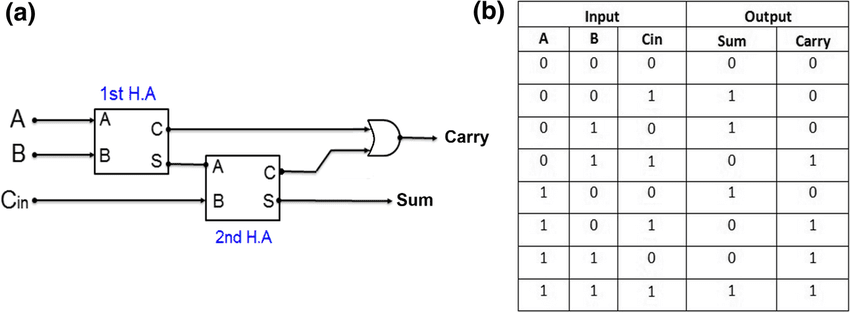

مدار تمام جمع کننده (Full Adder) یک مدار منطقی است که سه عدد باینری تک بیتی را با هم جمع می کند و در خروجی آن دو رقم باینری Sum و Carry تولید می شود. این ماژول را میتوان با استفاده از دو نیم جمع کننده و یک گیت OR ساخت. این مدار و جدول درستی آن در شکل زیر آمده است:

پیاده سازی ماژول تمام جمع کننده با وریلاگ verilog

در ادامه ماژول تمام جمع کننده پیاده سازی شده است. در این کد:

A و B و Cin ورودی هستند.

Sum و Cout خروجی می باشد.

این کد با استفاده از دو نیم جمع کننده و یک گیت OR پیاده سازی شده است.

module FullAdder(A, B, Cin, Sum, Cout);

input A, B, Cin;

output Sum, Cout;

wire S1, C1, C2;

// نیم جمع کننده اول

HalfAdder HA1(.A(A), .B(B), .Sum(S1), .Carry(C1));

// نیم جمع کننده دوم

HalfAdder HA2(.A(S1), .B(Cin), .Sum(Sum), .Carry(C2));

// رقم نقلی خروجی

or(Cout,C1,C2);

endmodule

پیاده سازی test bench تمام جمع کننده

تست بنچ ماژول نیم جمع کننده به این صورت است:

module FullAdder_tb;

reg A, B, Cin;

wire Sum, Cout;

// فراخوانی ماژول تمام جمع کننده

FullAdder UUT(.A(A), .B(B), .Cin(Cin), .Sum(Sum), .Cout(Cout));

// تعیین ورودیها

initial begin

// تست با ورودیهای مختلف

A = 0; B = 0; Cin = 0; #10

$display("A=%b, B=%b, Cin=%b, Sum=%b, Cout=%b", A, B, Cin, Sum, Cout);

A = 1; B = 0; Cin = 0; #10

$display("A=%b, B=%b, Cin=%b, Sum=%b, Cout=%b", A, B, Cin, Sum, Cout);

A = 0; B = 1; Cin = 0; #10

$display("A=%b, B=%b, Cin=%b, Sum=%b, Cout=%b", A, B, Cin, Sum, Cout);

A = 1; B = 1; Cin = 0; #10

$display("A=%b, B=%b, Cin=%b, Sum=%b, Cout=%b", A, B, Cin, Sum, Cout);

A = 0; B = 0; Cin = 1; #10

$display("A=%b, B=%b, Cin=%b, Sum=%b, Cout=%b", A, B, Cin, Sum, Cout);

A = 1; B = 0; Cin = 1; #10

$display("A=%b, B=%b, Cin=%b, Sum=%b, Cout=%b", A, B, Cin, Sum, Cout);

A = 0; B = 1; Cin = 1; #10

$display("A=%b, B=%b, Cin=%b, Sum=%b, Cout=%b", A, B, Cin, Sum, Cout);

A = 1; B = 1; Cin = 1; #10

$display("A=%b, B=%b, Cin=%b, Sum=%b, Cout=%b", A, B, Cin, Sum, Cout);

end

endmodule

خروجی ها به این صورت هستند:

A=0, B=0, Cin=0, Sum=0, Cout=0

A=1, B=0, Cin=0, Sum=1, Cout=0

A=0, B=1, Cin=0, Sum=1, Cout=0

A=1, B=1, Cin=0, Sum=0, Cout=1

A=0, B=0, Cin=1, Sum=1, Cout=0

A=1, B=0, Cin=1, Sum=0, Cout=1

A=0, B=1, Cin=1, Sum=0, Cout=1

A=1, B=1, Cin=1, Sum=1, Cout=1

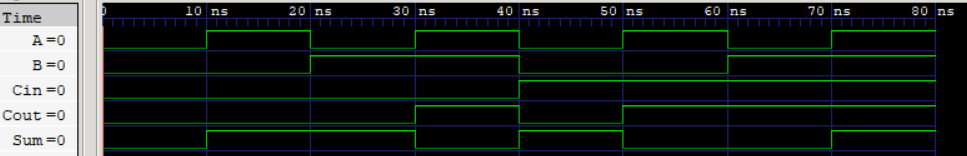

همچنین شکل موج خروجی ها به این صورت است:

سفارش انجام پروژه وریلاگ

اگر نیاز به کمک در انجام پروژه وریلاگ خود دارد، با ما در ارتباط باشید!